## A 50% Lower Power ARM Cortex CPU using DDC Technology with Body Bias

#### David Kidd August 26, 2013

Copyright © 2013 SuVolta, Inc. All rights reserved.

## Agenda

- DDC transistor and PowerShrink platform overview

- ARM Cortex-M0 implementation and results

- Application of DDC technology to HKMG nodes

Copyright © 2013 SuVolta, Inc. All rights reserved.

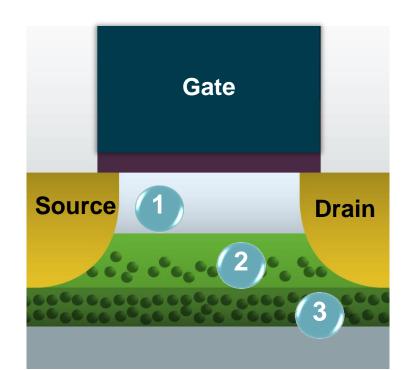

#### **Deeply Depleted Channel™ (DDC) Transistor**

#### Undoped/lightly doped region

- Improved matching (low RDF)

- Higher analog gain (↑ g<sub>m</sub>)

2

$V_{T}$  setting offset region

Multiple V<sub>T</sub> on chip

#### **Screening region**

- Superior scalability

- Improved drive current ( $\uparrow I_{eff} \downarrow DIBL$ )

- Strong body coefficient (corner pull-in)

One example, not drawn to scale

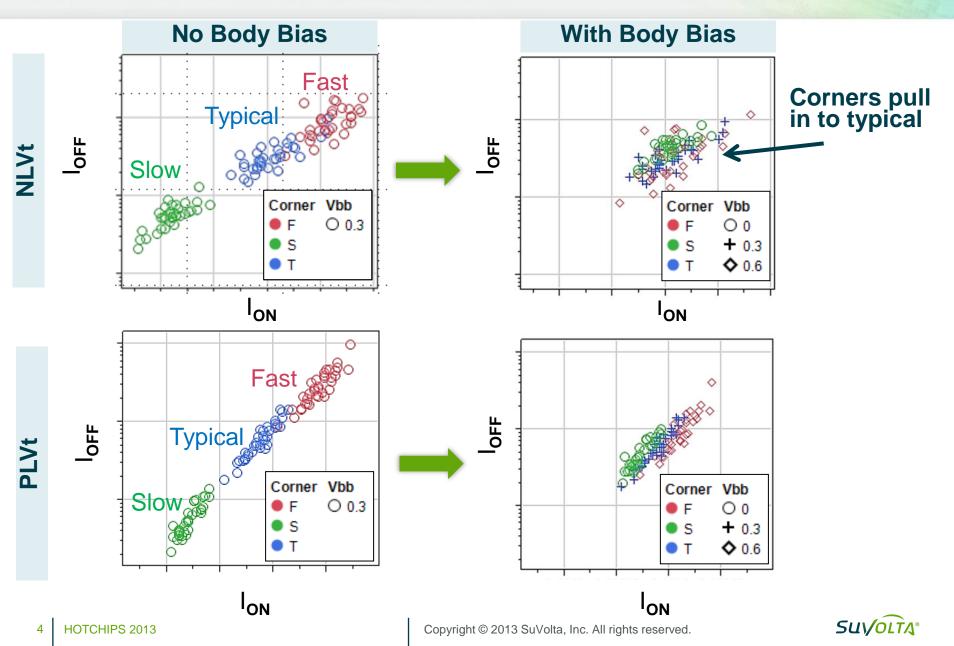

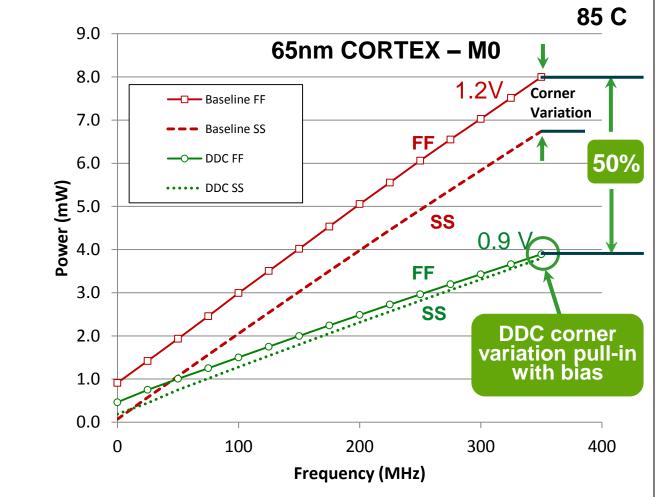

### **Corner Pull-in with Body Bias**

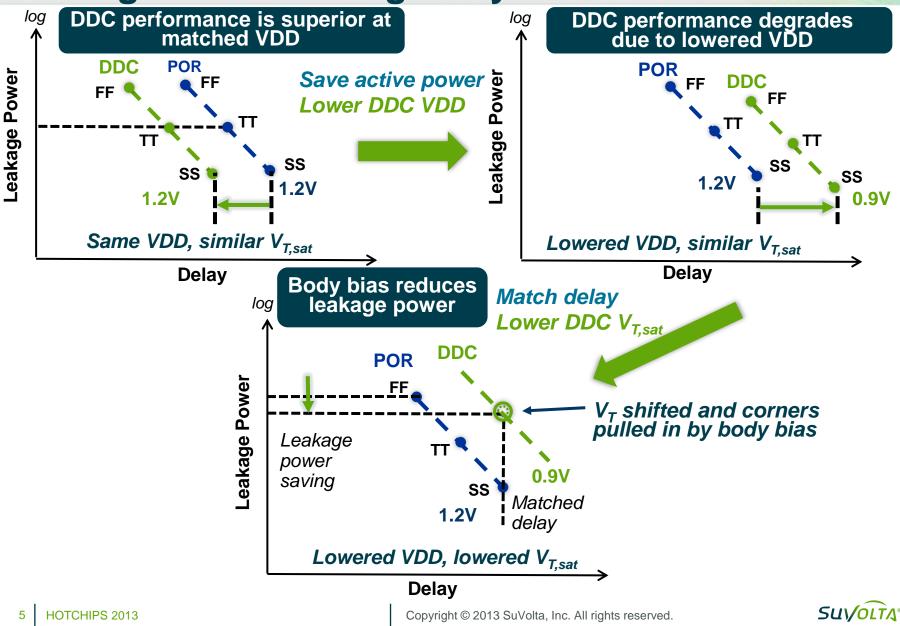

#### DDC PowerShrink Platform: Save Active and Leakage Power Using Body Bias

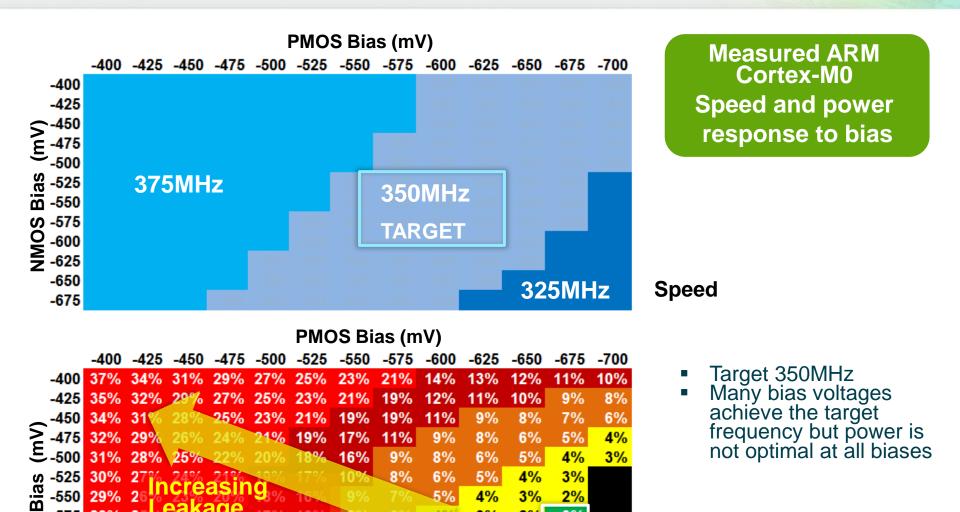

## **ARM Cortex-M0 CPU Bias Targeting**

3%

2%

1%

1%

4%

4%

2%

2%

1%

5%

4%

4%

3%

8%

7%

6%

5%

5%

10%

9%

8%

7%

7%

16%

10%

9%

9%

17%

18%

11%

20%

19%

20%

2%

1%

0%

Leakage (delta to optimal)

28%

27%

26%

25%

25% 22%

-575

-600

-625

-650

-675

NMOS

Copyright © 2013 SuVolta, Inc. All rights reserved.

Too Slow

0%

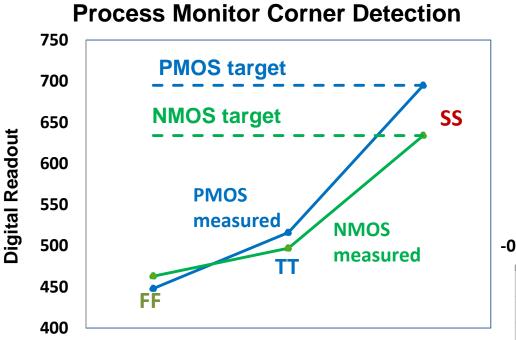

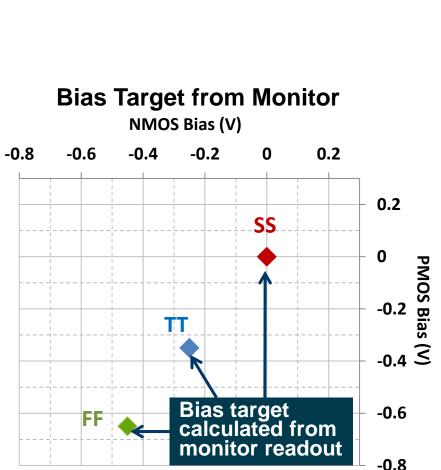

#### **Process Monitor Bias Targeting (55nm Measured)**

- Process Monitor independently measures NMOS and PMOS corners

- Digital readout correlates to corner

- Bias voltage is calculated from readout

SUV/OLTA

#### **Process Monitor Bias Targeting (55nm Measured)**

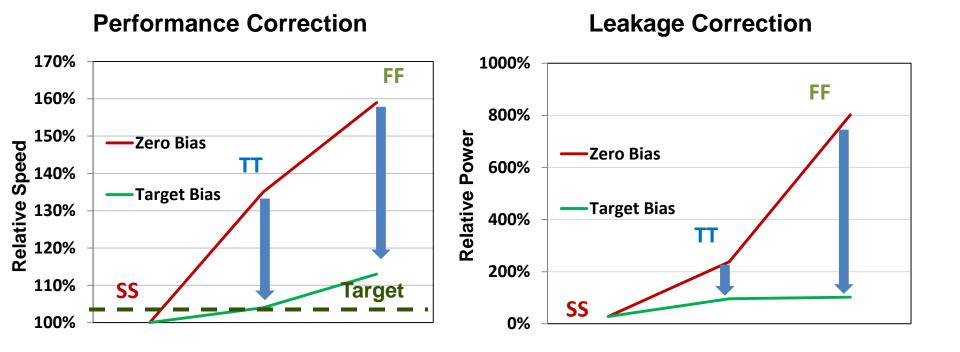

- Performance is corrected to 13% faster than target

- Fast corner leakage is corrected to the same point as typical

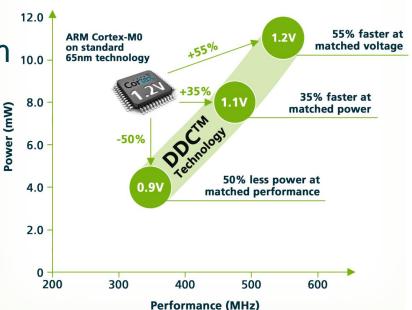

#### **PowerShrink Platform: ARM Cortex-M0 CPU**

- 50% power vs baseline at FF (leakage and dynamic)

- Matched performance at SS

9 HOTCHIPS 2013

Copyright © 2013 SuVolta, Inc. All rights reserved.

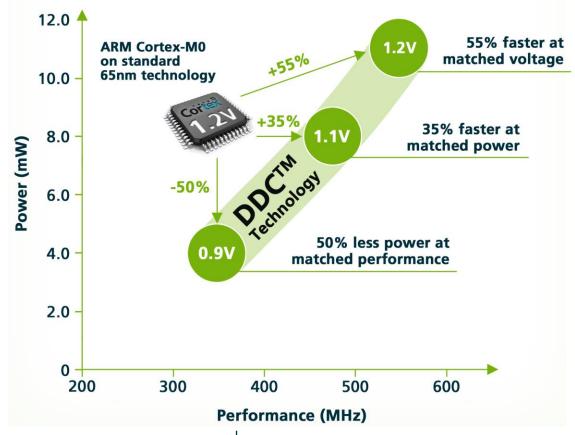

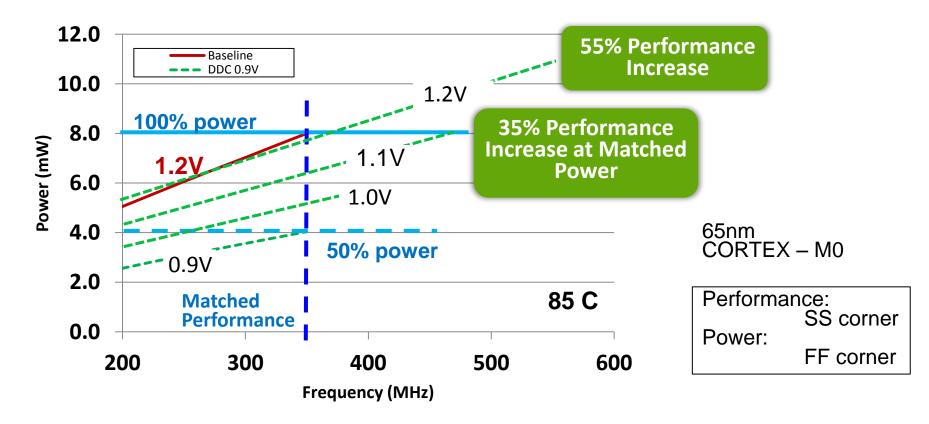

## **Tunable Power / Performance**

- Matched performance at 50% power

0.9V

- +35% performance at matched power

1.1V

- +55% performance at matched voltage 1.2V

SUV/OLTA

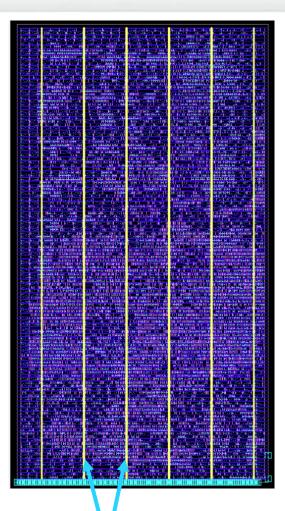

#### **ARM Cortex-M0 Body Bias Network Implementation**

- Minimal routing resources used for bias network

- Route in columns

- Double-space bias wires for reliability

- I PMOS wire, 1 NMOS wire

#### Vertical Track Usage per Column

| Layer | Available Tracks | Bias Tracks |

|-------|------------------|-------------|

| M2    | 300              | 4           |

| M4    | 300              | 0           |

| Total | 600              | 4 (0.7%)    |

#### **Bias Columns**

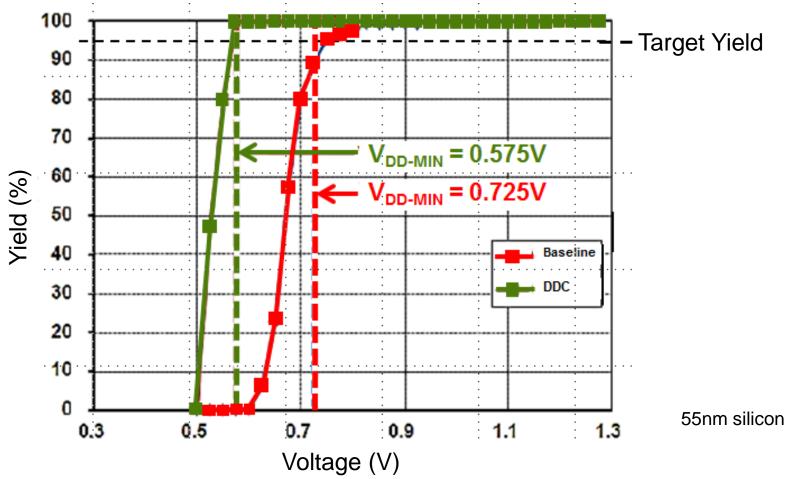

#### Lower SRAM V<sub>DD-min</sub> Enables Low-V<sub>DD</sub> Operation

- V<sub>DD-min</sub> of 8Mb SRAM lowered by 150mV at 125°C

- Production 55nm SRAM data

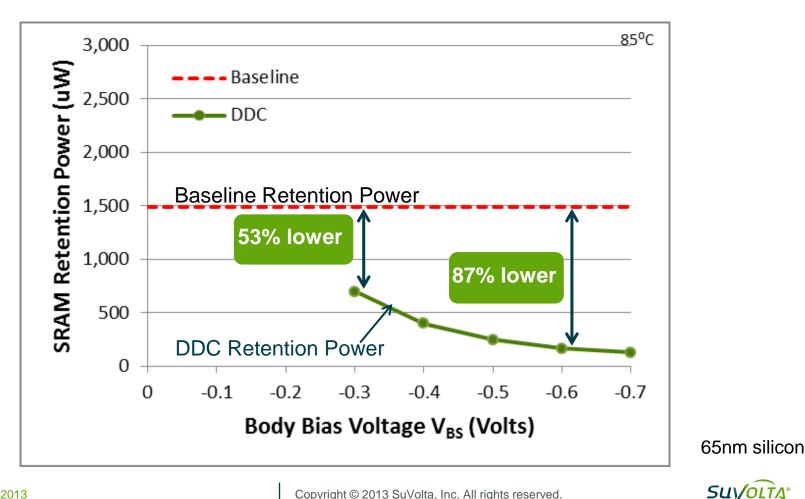

### **Lower SRAM Retention Power**

- 50% less leakage in Standby and Retention modes at nominal V<sub>BS</sub>

- More than 5X less leakage in Retention mode with  $V_{BS} = -0.6V$

13 **HOTCHIPS 2013**

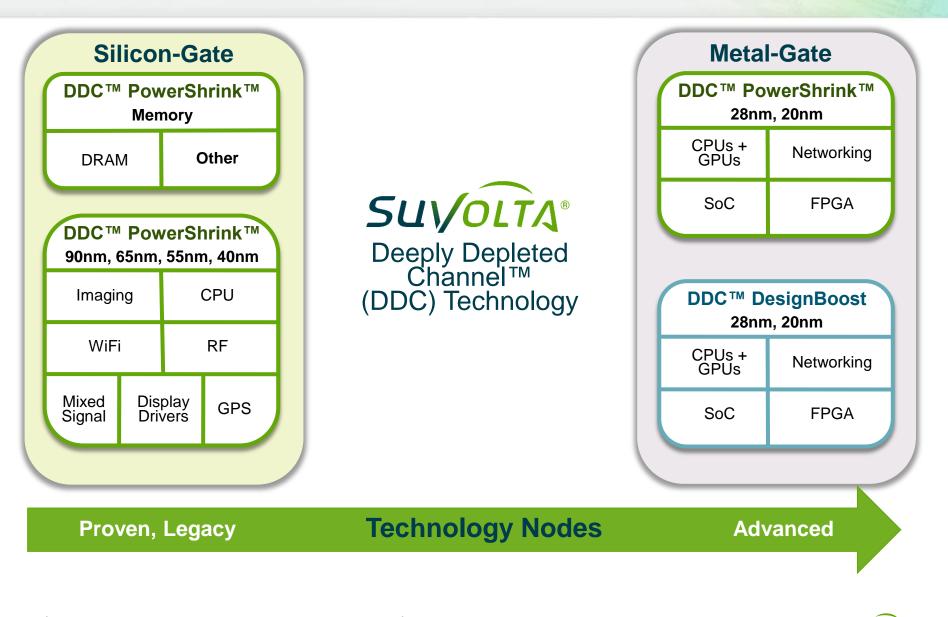

## **DDC Technology in Silicon Gate and HKMG**

SUV/OLTA®

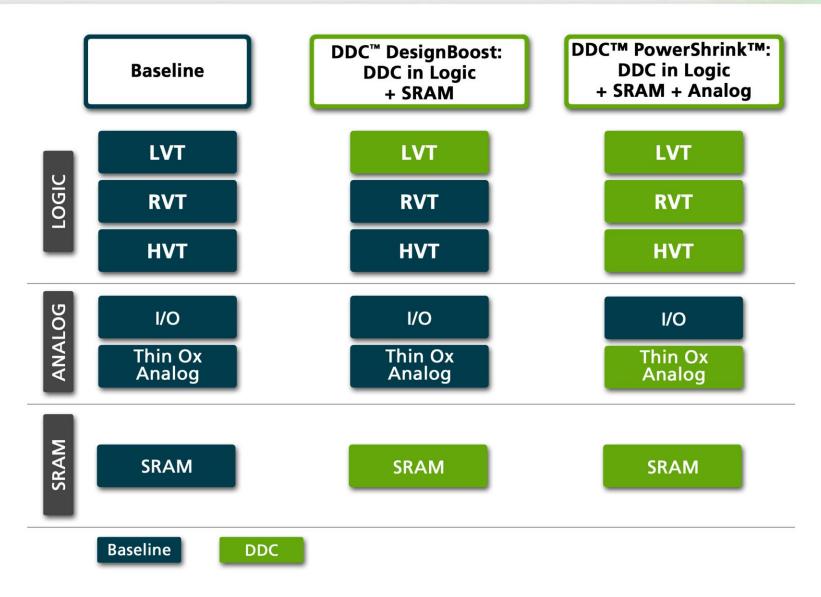

## **DDC Technology Modular Implementation**

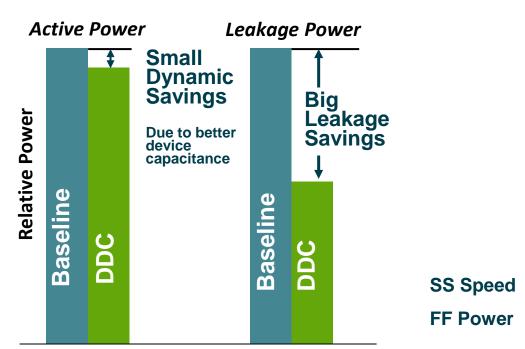

#### DDC DesignBoost: Target Leakage Power Savings

#### **DDC DesignBoost**

16 HOTCHIPS 2013

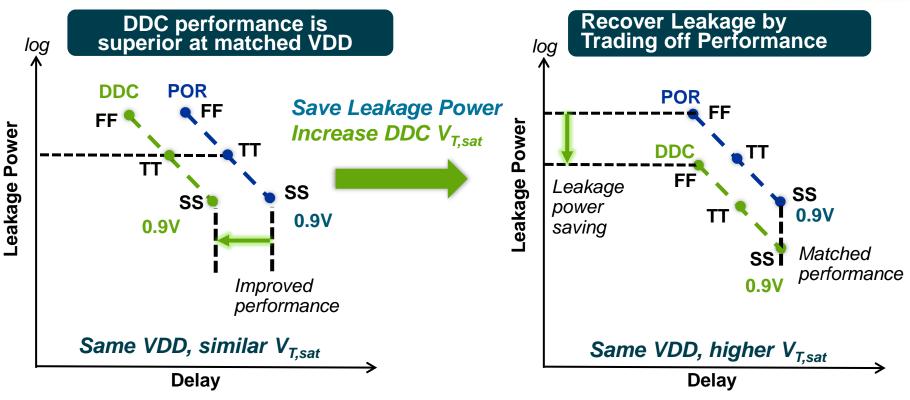

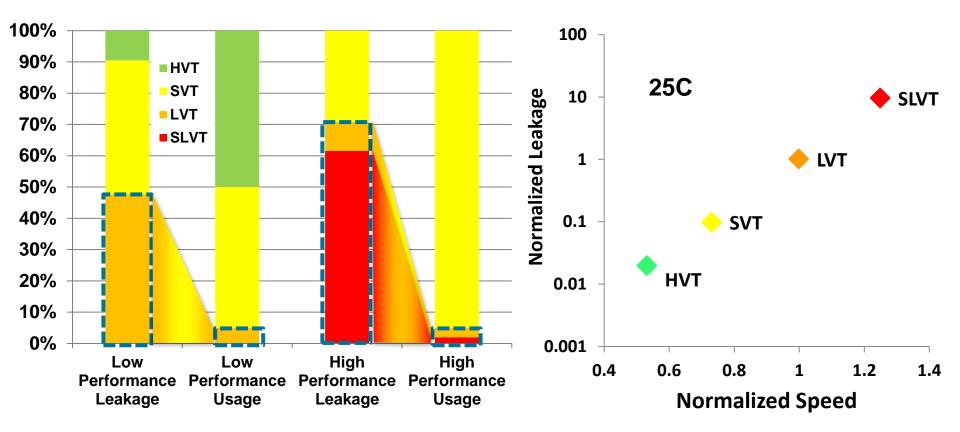

## **DDC DesignBoost Motivation**

- LVT and SLVT devices contribute a large portion of the leakage power at advanced nodes

- Leakage power reduction is a key value adder for high performance designs

#### **DDC DesignBoost Power Savings in HKMG**

#### **LVT Devices**

#### **DDC DesignBoost**

Target matched performance to reduce loff

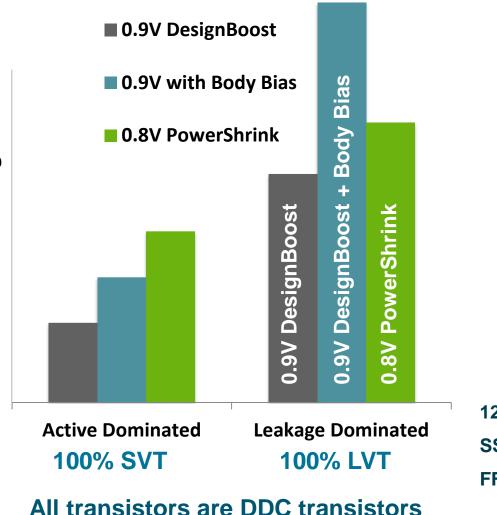

## **HKMG Power Analysis**

- HKMG design

- 10% activity factor

- DDC DesignBoost

- No design change

- Body Bias improves power savings

- PowerShrink platfrom

- For active power dominated circuits

125C SS Speed FF Power

#### 19 HOTCHIPS 2013

**Power Savings**

## Summary

- ARM Cortex-M0 validated at 65nm

- Matched performance at 50% power

- +35% performance at matched power

- +55% performance at matched voltage

- SRAM validated at 65nm and 55nm 10.0

- 150mV Vmin reduction in production 55nm SRAM

- Less than 50% static power in standby and retention

- DDC technology demonstrated at advanced HKMG nodes

- Lower static power at matched performance

- Lower active power with body bias

# SUV/OLTA®

Copyright © 2013 SuVolta, Inc. All rights reserved.